#### Review on Digital Design (Sequential Circuits)

University of South Carolina

Introduction to Computer Architecture Fall, 2024 Mehdi Yaghouti

University of South Carolina (M. Y.)

イロト イ団ト イヨト イヨト

## Storage Elements

- Maintains a binary state as long as power is on

- Provides control signals to switch the state

- Level sensitive storage elements: Latches

- Transition sensitive storage elements: Flip-Flops

- Latches are the building blocks of Flip-Flops

- Latches are useful for asynchronous designs

- Flip-Flops are the choice for synchronous circuits

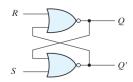

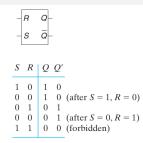

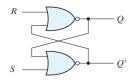

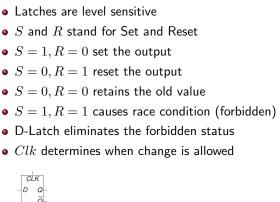

#### Latches

- Latches are level sensitive

- S and R stand for Set and Reset

- S = 1, R = 0 set the output

- S = 0, R = 1 reset the output

- S = 0, R = 0 retains the old value

- S = 1, R = 1 causes race condition (forbidden)

.

3/32

イロト イポト イヨト イヨト

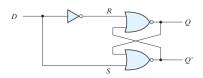

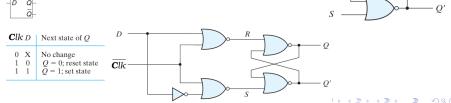

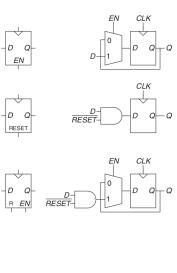

#### **D-Latches**

- Latches are level sensitive

- $\bullet \ S$  and R stand for Set and Reset

- S = 1, R = 0 set the output

- S = 0, R = 1 reset the output

- S = 0, R = 0 retains the old value

- S = 1, R = 1 causes race condition (forbidden)

- D-Latch eliminates the forbidden status

4/32

イロト イ団ト イヨト イヨト

#### **D-Latches**

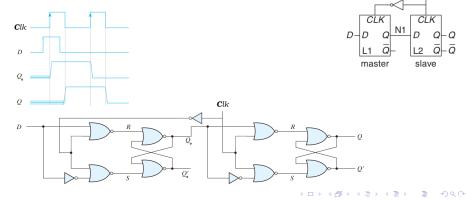

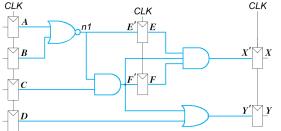

#### D Flip-Flop

- Master and Slave D-Latches connected back to back

- Master and Slave receives complementary clocks

- At Clk = 1, Master Latch is transparent

- At Clk = 0, Slave Latch is transparent

CLK

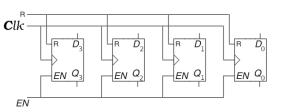

#### Register

CLK

- Enable determines whether data is loaded

- Reset clear the output to 0

- N-bit register is a bank of N Flip-Flops

イロト イ団ト イヨト イヨト

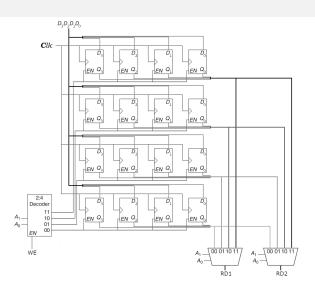

### Register File

- $4 \times 4$ -bits register file

- 2 Read ports

- 1 Write port

- $log_24$  address bus

CLK

A2

WD3

+5 +5

• 32×32-bits register file

WE3 RD1

Register

File

RD2

ヘロア 人間ア 人間ア 人間アー間

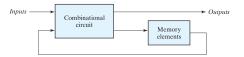

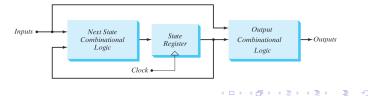

## Synchronous Sequential Circuits

- The outputs and the next state are both a function of the inputs

- The state of the system is hold in flip flops

イロン イ団 とく ヨン イヨン

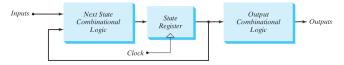

#### Finite State Machines

- Synchronous sequential circuits can be designed as Finite State Machines

- At each clock both the state and the output of the circuit will be updated

- The next state is computed based on both input and the current state

< □ > < 同 > < 三 > < 三 >

#### Finite State Machines

- Synchronous sequential circuits can be designed as Finite State Machines

- At each clock both the state and the output of the circuit will be updated

- The next state is computed based on both input and the current state

- There are two type of FSM

- Moore machines: The output depends directly only on the current state

イロト イポト イヨト イヨト

#### Finite State Machines

- Synchronous sequential circuits can be designed as Finite State Machines

- At each clock both the state and the output of the circuit will be updated

- The next state is computed based on both input and the current state

- There are two type of FSM

- Moore machines: The output depends directly only on the current state

• Mealy machines: The output depends on both current state and the input

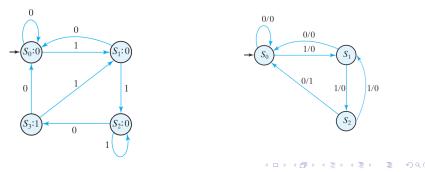

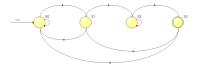

## State Diagram

#### • State Diagram:

A visual representation that depicts state transitions and outcomes in response to inputs

- States: Different conditions a system can be in

- Transitions: Arrows showing movement between states

- Inputs: Triggers for state changes

- Reset state: Start and end points of the process

- State Actions: Actions within states or during transitions

イロト イ団ト イヨト イヨト

### State Diagram

#### • State Diagram:

A visual representation that depicts state transitions and outcomes in response to inputs

- States: Different conditions a system can be in

- Transitions: Arrows showing movement between states

- Inputs: Triggers for state changes

- Reset state: Start and end points of the process

- State Actions: Actions within states or during transitions

< ロ > < 同 > < 回 > < 回 >

### State Diagram

#### • State Diagram:

A visual representation that depicts state transitions and outcomes in response to inputs

- States: Different conditions a system can be in

- Transitions: Arrows showing movement between states

- Inputs: Triggers for state changes

- Reset state: Start and end points of the process

- State Actions: Actions within states or during transitions

Assigning binary codes to sates

イロト イヨト イヨト イヨト

æ

• State coding is not unique and will affect the design

- Assigning binary codes to sates

- Obtain the binary-coded state table

| Present<br>State |   | Input | Next<br>State |   |  |

|------------------|---|-------|---------------|---|--|

| $S_1$ $S_0$      |   | x     | $S'_1$ S      |   |  |

| 0                | 0 | 0     | 0             | 0 |  |

| 0                | 0 | 1     | 0             | 1 |  |

| 0                | 1 | 0     | 0             | 0 |  |

| 0                | 1 | 1     | 1             | 0 |  |

| 1                | 0 | 0     | 1             | 1 |  |

| 1                | 0 | 1     | 1             | 0 |  |

| 1                | 1 | 0     | 0             | 0 |  |

| 1                | 1 | 1     | 0             | 1 |  |

イロト イヨト イヨト イヨト

- Assigning binary codes to sates

- Obtain the binary-coded state table

- Obtain the equations for flip flops inputs

|       | sent<br>ate | Input | Ne<br>Sta | ext<br>ate |

|-------|-------------|-------|-----------|------------|

| $S_1$ | $S_0$       | x     | $S'_1$    | $S_0'$     |

| 0     | 0           | 0     | 0         | 0          |

| 0     | 0           | 1     | 0         | 1          |

| 0     | 1           | 0     | 0         | 0          |

| 1     | 0           | 0     | 1         | 1          |

| 1     | 0           | 1     | 1         | 0          |

| 1     | 1           | 0     | 0         | 0          |

| 1     | 1           | 1     | 0         | 1          |

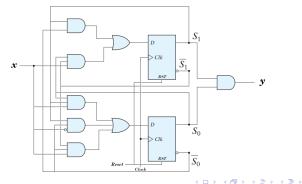

- Assigning binary codes to sates

- Obtain the binary-coded state table

- Obtain the equations for flip flops inputs

- Obtain the output equations in terms of states

| Present<br>State |       | Output |               |

|------------------|-------|--------|---------------|

| $S_1$            | $S_0$ | y      |               |

| 0                | 0     | 0      |               |

| 0                | 0     | 0      |               |

| 0                | 1     | 0      |               |

| 0                | 1     | 0      |               |

| 1                | 0     | 0      |               |

| 1                | 0     | 0      |               |

| 1                | 1     | 1      | $y = S_1 S_0$ |

| 1                | 1     | 1      |               |

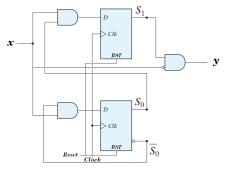

- Assigning binary codes to sates

- Obtain the binary-coded state table

- Obtain the equations for flip flops inputs

- Obtain the output equations in terms of states

- Oraw the logic circuit diagram

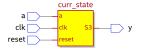

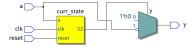

#### SystemVerilog

- Moore's FSM implementation

- typedef,always\_ff, always\_comb

```

typedef enum logic [1:0] {S0,S1,S2,S3} State;

State curr_state, next_state;

```

```

assign y = (state==S3);

endmodule

```

$$S_0 \to 00$$

$$S_1 \to 01$$

$$S_2 \to 10$$

イロト イヨト イヨト イヨト

æ

• State coding is not unique and will affect the design

- Assigning binary codes to sates

- Obtain the binary-coded state table

イロト イヨト イヨト イヨト

- Assigning binary codes to sates

- Obtain the binary-coded state table

- Obtain the equations for flip flops inputs and outputs

| Present<br>State |       |          |        | ext<br>ate | Output |                                                                                                     |

|------------------|-------|----------|--------|------------|--------|-----------------------------------------------------------------------------------------------------|

| $S_1$            | $S_0$ | <i>x</i> | $S'_1$ | $S_0'$     | У      |                                                                                                     |

| 0                | 0     | 0        | 0      | 0          | 0      |                                                                                                     |

| 0                | 0     | 1        | 0      | 1          | 0      |                                                                                                     |

| 0                | 1     | 0        | 0      | 0          | 0      |                                                                                                     |

| 0                | 1     | 1        | 1      | 0          | 0      | $S_0' = \overline{S}_0 x$                                                                           |

| 1                | 0     | 0        | 0      | 0          | 1      | $S'_0 = \overline{S}_0 \mathbf{x}$ $S'_1 = S_0 \mathbf{x}$ $\mathbf{y} = S_1 \overline{\mathbf{x}}$ |

| 1                | 0     | 1        | 0      | 1          | 0      | $S_1 = S_0 \boldsymbol{x}$                                                                          |

| 1                | 1     | x        | х      | х          | ×      | $y = S_1 \overline{x}$                                                                              |

- Assigning binary codes to sates

- Obtain the binary-coded state table

- Obtain the equations for flip flops inputs and outputs

- Oraw the logic circuit diagram

イロト イ団ト イヨト イヨト

## SystemVerilog

#### Mealy's FSM implementation

| ( input | logic          | clk,                       |                                                                                               |

|---------|----------------|----------------------------|-----------------------------------------------------------------------------------------------|

| input   | logic          | reset,                     |                                                                                               |

| input   | logic          | a,                         |                                                                                               |

| output  | logic          | y );                       |                                                                                               |

|         | input<br>input | input logic<br>input logic | <pre>( input logic clk,<br/>input logic reset,<br/>input logic a,<br/>output logic y );</pre> |

typedef enum logic [1:0] {S0,S1,S2} State; State curr\_state, next\_state;

```

always_comb

case (curr_state)

S0: 1f (a) next_state = S1;

else next_state = S0;

S1: 1f (a) next_state = S2;

else next_state = S0;

default: next_state = S0;

```

```

endcase

```

```

always comb

```

```

case (curr_state)

S0: y = 1'b0;

S1: y = 1'b0;

S2: y = (a) ? 1'b0 : 1'b1;

default: y = 1'b0;

endcase

```

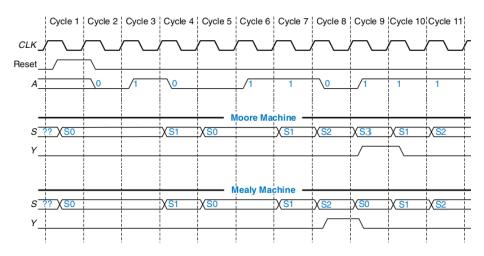

## **Timing Diagram**

University of South Carolina (M. Y.)

23 / 32

イロト イヨト イヨト イヨト

イロト イヨト イヨト イヨト

24 / 32

.

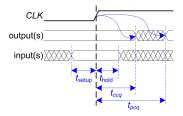

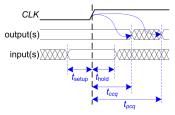

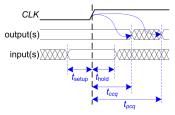

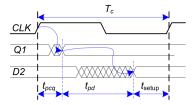

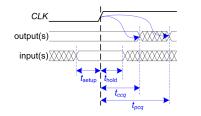

•  $t_{setup}$ : It's the time input must have stabilized, before the rising edge

イロト イヨト イヨト イヨト

- $t_{setup}$ : It's the time input must have stabilized, before the rising edge

- $t_{hold}$  : It's the time input must have stabilized, after the rising edge

- $t_{setup}$ : It's the time input must have stabilized, before the rising edge

- $t_{hold}$  : It's the time input must have stabilized, after the rising edge

- $t_{apr}$  : It's the sum  $t_{setup} + t_{hold}$

イロト イ団ト イヨト イヨト

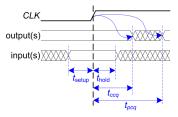

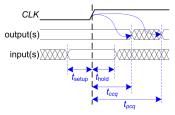

- $t_{setup}$ : It's the time input must have stabilized, before the rising edge

- $t_{hold}$  : It's the time input must have stabilized, after the rising edge

- $t_{apr}$  : It's the sum  $t_{setup} + t_{hold}$

- $t_{ccq}$ : It's the contamination delay from the clock to output of the flip flops

イロト イ団ト イヨト イヨト

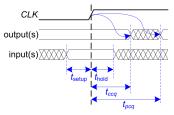

- $t_{setup}$ : It's the time input must have stabilized, before the rising edge

- $t_{hold}$  : It's the time input must have stabilized, after the rising edge

- $t_{apr}$  : It's the sum  $t_{setup} + t_{hold}$

- $t_{ccq}$ : It's the contamination delay from the clock to output of the flip flops

- $t_{pcq}$ : It's the propagation delay from the clock to output of the flip flops

イロト イ団ト イヨト イヨト

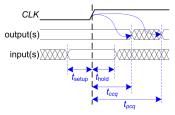

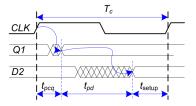

- t<sub>setup</sub>: It's the time input must have stabilized, before the rising edge

- $t_{hold}$  : It's the time input must have stabilized, after the rising edge

- $t_{apr}$  : It's the sum  $t_{setup} + t_{hold}$

- $t_{ccq}$ : It's the contamination delay from the clock to output of the flip flops

- $t_{pcq}$ : It's the propagation delay from the clock to output of the flip flops

- The clock cycle  $T_c$  must be long enough for all the signals to be settled

イロト イヨト イヨト イヨト

- $t_{setup}$ : It's the time input must have stabilized, before the rising edge

- $t_{hold}$  : It's the time input must have stabilized, after the rising edge

- $t_{apr}$  : It's the sum  $t_{setup} + t_{hold}$

- $t_{ccq}$ : It's the contamination delay from the clock to output of the flip flops

- $t_{pcq}$ : It's the propagation delay from the clock to output of the flip flops

- The clock cycle  $T_c$  must be long enough for all the signals to be settled

- The clock frequency is given by  $F_c = \frac{1}{T_c}$

イロト イポト イヨト イヨト

- $t_{setup}$ : It's the time input must have stabilized, before the rising edge

- $t_{hold}$  : It's the time input must have stabilized, after the rising edge

- $t_{apr}$  : It's the sum  $t_{setup} + t_{hold}$

- $t_{ccq}$ : It's the contamination delay from the clock to output of the flip flops

- $t_{pcq}$ : It's the propagation delay from the clock to output of the flip flops

- The clock cycle  $T_c$  must be long enough for all the signals to be settled

- The clock frequency is given by  $F_c = \frac{1}{T_c}$

イロト イポト イヨト イヨト

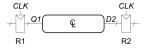

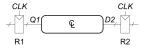

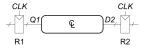

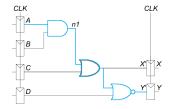

• Determine the minimum clock cycle in the following circuit

イロト イヨト イヨト イヨト

• Determine the minimum clock cycle in the following circuit

Based on the following timing constraints,

イロト イヨト イヨト イヨト

• Determine the minimum clock cycle in the following circuit

Based on the following timing constraints,

We must have:

$$T_c \ge t_{pcq} + t_{pd} + t_{setup}$$

イロト イヨト イヨト イヨト

• Determine the minimum clock cycle in the following circuit

Based on the following timing constraints,

CLK

We must have:

$$T_c \ge t_{pcq} + t_{pd} + t_{setup}$$

$$t_{hold} \le t_{ccq} + t_{cd}$$

イロト イヨト イヨト イヨト

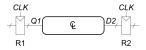

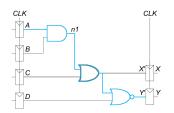

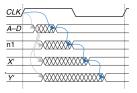

• Determine the max and min delay for the given circuit

イロト イヨト イヨト イヨト

.

• Determine the max and min delay equation for the given circuit

イロト イヨト イヨト イヨト

• Determine the max and min delay equation for the given circuit

$T_c \ge t_{pcq} + 3 t_{pd} + t_{setup}$

イロン イ団 とくほとう ほんし

.

• Determine the max and min delay equation for the given circuit

- $T_c \ge t_{pcq} + 3\,t_{pd} + t_{setup}$

- $t_{hold} \leq t_{ccq} + t_{cd}$

#### Question

• Determine the maximum  $F_c$  and maximum tolerable  $t_{hold}$  for the following circuit

| Flip Flop  | $t_{ccq}$ (ps) | $t_{pcq}$ (ps) | tseti   | up (ps) | t <sub>hold</sub> (ps) |

|------------|----------------|----------------|---------|---------|------------------------|

|            | 30             | 80             |         | 50      | ?                      |

| Gate       | $t_{p_s}$      | (ps) t         | cd (ps) |         |                        |

| 2-input NA | AND 20         | ) :            | 15      |         |                        |

| 3-input NA | AND 30         | ) 2            | 25      |         |                        |

| 2-input NO | DR 30          | ) 2            | 25      |         |                        |

| 2-input OF | <b>ξ</b> 4(    | ) (            | 30      |         |                        |

æ

$$F_{max} = ?$$

$t_{hold} = ?$

イロト イ団ト イヨト イヨト