### Number Representation and Computer Arithmetic

University of South Carolina

Introduction to Computer Architecture Fall, 2024 Mehdi Yaghouti

## Binary Number Representation

#### Decimal system:

- Base: 10

- Digits:  $\{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$

- Representation of a decimal number:

```

1's column

10's column

100's column

1000's columr

```

| $9742_{10} = 9 \times 10^3$ | $+7 \times 10^{2}$ | + 4 × 10 <sup>1</sup> | $+ 2 \times 10^{0}$ |

|-----------------------------|--------------------|-----------------------|---------------------|

| nine                        | seven              | four                  | two                 |

| thousands                   | hundreds           | tens                  | ones                |

#### • Binary system:

- Base: 2

- Digits: {0,1}

- Representation of a binary number:

1's column 2's column 4's column 8's column 16's column

$$10110_2 = 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 = 22_{10}$$

イロト イヨト イヨト イヨト

æ

## **Unsigned Binary Numbers**

- N-bit binary number can represent  $2^N$  numbers,

- Minimum:  $\overbrace{0\ldots0}^{\text{N-bits}}$

- Maximum: 1...1

- Range:  $\left[0, \ldots, 2^N 1\right]$

- Decimal to binary conversion

- Using common powers of 2 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096

- Repeated Divisions

- Binary to decimal conversion  $(b_N \dots b_0)_2 = \sum_{k=0}^N 2^k b_k$

| 4-Bit<br>Binary<br>Numbers | Decimal<br>Equivalents |

|----------------------------|------------------------|

| 0000                       | 0                      |

| 0001                       | 1                      |

| 0010                       | 2                      |

| 0011                       | 3                      |

| 0100                       | 4                      |

| 0101                       | 5                      |

| 0110                       | 6                      |

| 0111                       | 7                      |

| 1000                       | 8                      |

| 1001                       | 9                      |

| 1010                       | 10                     |

| 1011                       | 11                     |

| 1100                       | 12                     |

| 1101                       | 13                     |

| 1110                       | 14                     |

| 1111                       | 15                     |

イロト イヨト イヨト イヨト

3

## Hexadecimal Representation

#### Hexadecimal system:

- Base: 16

- Digits: {0,1,2,3,4,5,6,7,8,9,*A*,*B*,*C*,*D*,*E*,*F*}

- Representation of a hexadecimal number:

1's column 16's column 256's columr

$\begin{array}{c} 2ED_{16} = 2 \times 16^2 + E \times 16^1 + D \times 16^0 = 749_{10} \\ \\ two \\ two hundred fifty six's \\ sixteens \\ \end{array}$

- Correspondence between Hex digits and 4-bits  $\sum_{k=0}^{N} 2^k b_k = \sum_{k=0}^{N/4} 16^k \left( \sum_{l=0}^3 2^l b_{(4*k+l)} \right)$

- Binary to Hexadecimal conversion

- Pack each 4-bit into a hex digit

- Hexadecimal to Binary conversion

- Unpack each hex digits into 4-bits

#### DEAFDAD8 = 1101 1110 1010 1111 1101 1010 1101 1000

| Hexadecimal Digit | Binary Equivalent |

|-------------------|-------------------|

| 0                 | 0000              |

| 1                 | 0001              |

| 2                 | 0010              |

| 3                 | 0011              |

| 4                 | 0100              |

| 5                 | 0101              |

| 6                 | 0110              |

| 7                 | 0111              |

| 8                 | 1000              |

| 9                 | 1001              |

| А                 | 1010              |

| В                 | 1011              |

| С                 | 1100              |

| D                 | 1101              |

| Е                 | 1110              |

| F                 | 1111              |

4/4

3

## Octal Representation

- Octal system:

- Base: 8

- Digits:  $\{0, 1, 2, 3, 4, 5, 6, 7\}$

- Representation of an octal number:

1's column 8's column 64's column

$$367_8 = 3 \times 8^2 + 6 \times 8^1 + 7 \times 8^0 = 247_{10}$$

- Correspondence between Octal digits and 3-bits  $\sum_{k=0}^{N} 2^k b_k = \sum_{k=0}^{N/3} 8^k \left( \sum_{l=0}^3 2^l b_{(3*k+l)} \right)$

- Binary to Octal conversion

- Pack each 3-bit into a octal digit

- Octal to Binary conversion

- Unpack each octal digits into 3-bits

$$(2357)_8 = 010 \ 011 \ 101 \ 111$$

| Octal Digit | Binary Equivalent |

|-------------|-------------------|

| 0           | 000               |

| 1           | 001               |

| 2           | 010               |

| 3           | 011               |

| 4           | 100               |

| 5           | 101               |

| 6           | 110               |

| 7           | 111               |

| 7           | 111               |

イロト イヨト イヨト イヨト

## **Binary Addition**

#### • Basic Rules:

- 0 + 0 = 0

- 0 + 1 = 1

- 1 + 0 = 1

- 1 + 1 = 10 (0 with a carry of 1)

#### • Steps for Adding Two Binary Numbers:

- Aligning the Numbers

- Adding digit by digit, starting from LSB

- Ocarry Over: If the sum is 2 (binary 10), carry the 1 to the next column

- Overflow: The carry out of the leftmost digit

• Care must be taken as registers have constant number of bits

-

イロト イヨト イヨト イヨト

3

## **Binary Subtraction**

#### Basic Rules:

- 0 0 = 0

- 1 0 = 1

- 1 1 = 0

- 0 1 = 1 (with a borrow of 1 from the next higher bit)

#### • Steps for Subtracting Two Binary Numbers:

- Aligning the numbers

- O Subtracting digit by digit, starting from LSB

- **③** Borrowing: When subtracting 1 from 0, borrow 1 from the next higher bit

- O Borrow in: If a borrow needed beyond the leftmost digit, the result is negative

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ ― 三 ● ○○○

## Sign/Magnitude Number System

#### • Sign/Magnitude:

• Sign bit: Most significant bit

$$\begin{cases} + \to 0 \\ - \to 1 \end{cases}$$

Example:

+23 = 00010111 $-23 = 10010111 \qquad (sign/magnitude representation)$

- Spans the range  $\left[-\left(2^{N-1}-1

ight),2^{N-1}-1

ight]$

- Ordinary addition doesn't work on sign included representation

- Zero has two representations +0, -0

- Troublesome to use in fast arithmetic circuits

<ロ> <四> <四> <四> <四> <四> <四</p>

#### University of South Carolina (M. Y.)

## Two's Complement Number System

#### • Two's Complement system:

• N-bits Two's complement representation

$$(b_{N-1}\dots b_0)_2 = -b_N 2^{N-1} + \sum_{k=0}^{N-2} 2^k b_k$$

- $\bullet~{\rm Spans}$  the asymmetric range  $\left[-\,2^{N-1},2^{N-1}-1\right]$

- Ordinary addition works well on sign included representation

- Sign bit: Most significant bit

$$\begin{cases} + \to 0 \\ - \to 1 \end{cases}$$

- Zero has only one representation

- Two's complement is the most accepted one for fast arithmetic circuits

| Decimal<br>Representation | Twos Complement<br>Representation |

|---------------------------|-----------------------------------|

| +8                        | -                                 |

| +7                        | 0111                              |

| +6                        | 0110                              |

| +5                        | 0101                              |

| +4                        | 0100                              |

| +3                        | 0011                              |

| +2                        | 0010                              |

| +1                        | 0001                              |

| 0                         | 0000                              |

| -1                        | 1111                              |

| -2                        | 1110                              |

| -3                        | 1101                              |

| -4                        | 1100                              |

| -5                        | 1011                              |

| -6                        | 1010                              |

| -7                        | 1001                              |

| -8                        | 1000                              |

9/4

◆□▶ ◆圖▶ ◆臣▶ ◆臣▶ ○臣○

## Two's Complement System

- Negation Rule

- Negate all the bits

Add 1

- Example:

$\begin{array}{l} +23 = 00010111 \xrightarrow{\text{negated}} 11101000 \xrightarrow{+1} 11101001 = -23 \\ -23 = 11101001 \xrightarrow{\text{negated}} 00010110 \xrightarrow{+1} 00010111 = +23 \end{array}$

#### Addition/Subtraction

| 47 + 11 = 58 | 47 - 11 = 36 | -47 + 11 = -36 | -47 - 11 = -58 |

|--------------|--------------|----------------|----------------|

| 00101111     | 00101111     | 11010001       | 11010001       |

| +00001011    | + 11110101   | +00001011      | + 11110101     |

| 00111010     | 100100100    | 11011100       | 111000110      |

### Overflow

#### Unsigned Numbers

• Overflow occurs when there is a carry out of the MSB column Example:

7 + 12 = 19 0111 + 1100 11011

#### • Signed Numbers (Two's complement)

- Overflow can only happen when two numbers have the same sign bit

- Overflow occurs when the result has the opposite sign bit

Example:

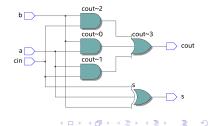

• Half Adder:  $\{c_{out}, S\} = A + B$

イロン イ団 とく ヨン イヨン

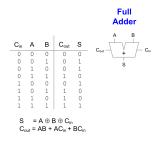

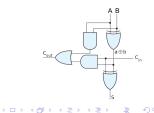

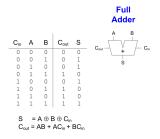

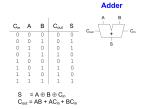

- Half Adder:  $\{c_{out}, S\} = A + B$

- Full Adder:  $\{c_{out}, S\} = A + B + c_{in}$

- Generate:  $G = A \bullet B$

- **Propagate:**  $P = A \oplus B$

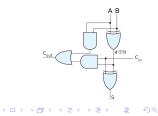

- Half Adder:  $\{c_{out}, S\} = A + B$

- Full Adder:  $\{c_{out}, S\} = A + B + c_{in}$

- Generate:  $G = A \bullet B$

- Propagate:  $P = A \oplus B$

- Delay:

$max\{2t_{pd\_xor}, t_{pd\_xor} + t_{pd\_or} + t_{pd\_and}\}$

|        |   |   |                                           |      | Full<br>Adder |

|--------|---|---|-------------------------------------------|------|---------------|

| Cin    | A | в | Cout                                      | s    |               |

| 0      | 0 | 0 | 0                                         | 0    | + Cin         |

| 0      | 0 | 1 | 0                                         | 1    | s             |

| 0      | 1 | 0 | 0                                         | 1    | 3             |

| 0      | 1 | 1 | 1                                         | 0    |               |

| 1      | 0 | 0 | 0                                         | 1    |               |

| 1      | 0 | 1 | 1                                         | 0    |               |

| 1      | 1 | 0 | 1                                         | 0    |               |

| 1      | 1 | 1 | 1                                         | 1    |               |

| S<br>C |   |   | 3 ⊕ C <sub>in</sub><br>AC <sub>in</sub> + | BCin |               |

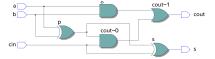

- Half Adder:  $\{c_{out}, S\} = A + B$

- Full Adder:  $\{c_{out}, S\} = A + B + c_{in}$

- Generate:  $G = A \bullet B$

- Propagate:  $P = A \oplus B$

- Delay:  $max\{2 t_{pd\_xor}, t_{pd\_xor} + t_{pd\_or} + t_{pd\_and}\}$

•

$$t_{FA} = t_{pd\_or3} + t_{pd\_and}$$

## SystemVerilog (Optional)

• Implementation using P and G signals

. . . . . . .

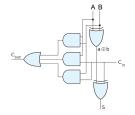

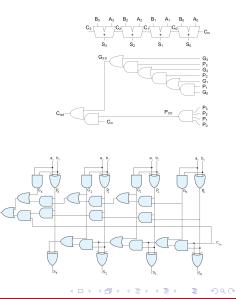

### **Ripple-Carry Adder**

- Carry Propagate Adder (CPA): Sums N-bit inputs

- Ripple-Carry Adder: Chains N full adders

• Delay:

$$t_{pd\_rca} = N_t t_{FA}$$

Full

æ

17/49

イロト イ団ト イヨト イヨト

## Look-ahead Block

#### • Generate:

$$G_{j:i} = G_j + P_j \, G_{j-1:i}$$

• Propagate:

$$P_{j:i} = P_j P_{j-1} \dots P_i$$

### • Carry:

$$C_{out} = G_{j:i} + P_{j:i}C_{in}$$

### • Delay:

$$t_{pg} = max\{t_{AND}, t_{XOR}\}$$

$$t_{pg,block} = 3 \ (t_{AND} + t_{OR})$$

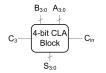

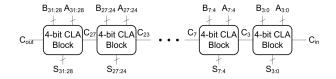

### Carry Look-Ahead Adder

- Generate:  $G_{j:i} = G_j + P_j G_{j-1:i}$

- Propagate:  $P_{j:i} = P_j P_{j-1} \dots P_i$

- Delay:  $t_{cla} = t_{pg} + t_{pg\_block} + \left(\frac{N}{k} 1\right) t_{and\_or} + k t_{FA}$

イロト イポト イヨト --

.

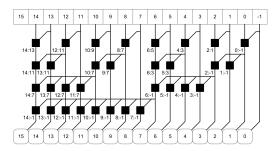

## Prefix Adder (Optional)

- Generate:  $G_{i:j} = G_{i:k} + P_{i:k} G_{k-1:j}$

- Propagate:  $P_{i:j} = P_{i:k} P_{k-1:j}$

- Delay:  $t_{PA} = t_{pg} + t_{pg-prefix} \log_2 N + t_{XOR}$

.

イロト イヨト イヨト イヨト

### Question

• Compare the delays of a 64-bit ripple-carry, a 64-bit carry-lookahead with 4-bit blocks and a 64-bit prefix adder.

| Gate         | $t_{pd}$ (ps) | $t_{cd}$ (ps) |

|--------------|---------------|---------------|

| NOT          | 15            | 10            |

| 2-input NAND | 20            | 15            |

| 3-input NAND | 30            | 25            |

| 2-input NOR  | 30            | 25            |

| 3-input NOR  | 45            | 35            |

| 2-input AND  | 30            | 25            |

| 3-input AND  | 40            | 30            |

| 2-input OR   | 40            | 30            |

| 3-input OR   | 55            | 45            |

| 2-input XOR  | 60            | 40            |

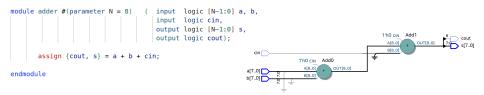

## SystemVerilog (Optional)

- keyword parameter

- Using high level description we leave the implementation to the synthesizer

æ

## Subtraction

- Two's Complement

- Subtraction:  $A B = A + \overline{B} + 1$

イロト イヨト イヨト イヨト

23 / 49

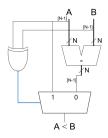

### Comparators

- Compares two binary inputs

- Using XNOR to check equality

- Using subtraction and check the sign bit

イロト イヨト イヨト イヨト

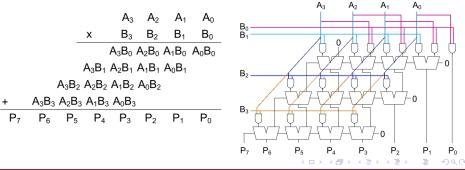

### Multiplication

- Binary multiplication is based on two basic operations:

- Generation of partial products

- Accumulation

- The multiplication of two N-bits number is in general a 2N-bits number

|   |   |   | × | _ | _ | 0<br>1 | _ |

|---|---|---|---|---|---|--------|---|

|   |   |   | _ | 0 | 0 | 0      | 0 |

|   |   |   | 1 | 1 | 0 | 1      |   |

|   |   | 1 | 1 | 0 | 1 |        |   |

| + | 1 | 1 | 0 | 1 |   |        |   |

| 1 | 0 | 1 | 1 | 0 | 1 | 1      | 0 |

イロト イヨト イヨト イヨト

.

### Multiplication

- Binary multiplication is based on two basic operations:

- Generation of partial products

- Accumulation

- The multiplication of two N-bits number is a 2N-bits number in general

- Each partial product is either zero or the multiplicand

イロン イ団 とく ヨン イヨン

.

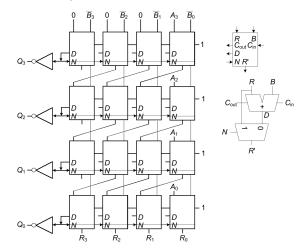

### Array Multiplier

- Binary multiplication is based on two basic operations:

- Generation of partial products

- Accumulation

- The multiplication of two N-bits number is a 2N-bits number in general

- Each partial product is either zero or the multiplicand

- Partial products can be generated by using AND gates

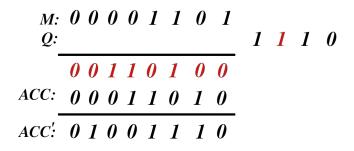

- Binary multiplication can be done in a sequential manner

- Sequential multiplication is based on two observations

- Each partial product is either zero of the multiplicand

- The partial products can be accumulated incrementally

- It can be best understood by an example

## ACC: 0 0 0 0 0 0 0 0 0

3

- Binary multiplication can be done in a sequential manner

- Sequential multiplication is based on two observations

- Each partial product is either zero of the multiplicand

- The partial products can be accumulated incrementally

- It can be best understood by an example

イロト イヨト イヨト イヨト

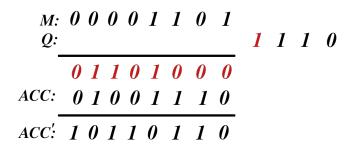

- Binary multiplication can be done in a sequential manner

- Sequential multiplication is based on two observations

- Each partial product is either zero of the multiplicand

- The partial products can be accumulated incrementally

- It can be best understood by an example

- Binary multiplication can be done in a sequential manner

- Sequential multiplication is based on two observations

- · Each partial product is either zero of the multiplicand

- The partial products can be accumulated incrementally

- It can be best understood by an example

イロト 不得 トイヨト イヨト

- Binary multiplication can be done in a sequential manner

- Sequential multiplication is based on two observations

- · Each partial product is either zero of the multiplicand

- The partial products can be accumulated incrementally

- It can be best understood by an example

イロト 不得 トイヨト イヨト

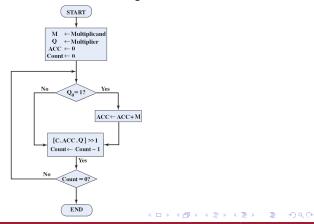

- Binary multiplication can be done in a sequential manner

- Sequential multiplication is based on two observations

- Each partial product is either zero of the multiplicand

- The partial products can be accumulated incrementally

- The process can be described with the following flowchart

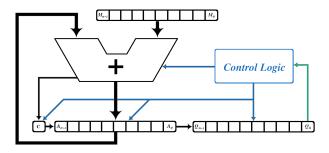

- Hardware Architecure

- M holds the multplicand

- Q holds the multiplier

- A holds the partial products summation

## SystemVerilog Project: Sequential Multiplier (Optional)

- Design a system verilog module to perform the sequential multiplication

- Your module must have the following interface

endmodule

- The project is optional and has extra bonus

- The following files must be uploaded

- The multiplier module: *Seq\_Multiplier.sv*

- Testbench: Testbench.sv

- Simulated Waveforms: Waveforms.pdf

- Comparing the sequential and array multiplier regarding the delay time and resource requirements

イロト イヨト イヨト イヨト

):

3

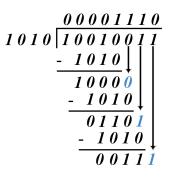

# Division (Optional)

- Binary division is based on two basic operations:

- Generation of partial remainders

- Subtraction and shifting

- The quotient in division of two N-bits number is in general a N-bits number

$$\begin{array}{c}

0 & 0 & 0 & 0 & 1 & 1 & 1 & 0 \\

1 & 0 & 1 & 0 & 1 & 0 & 0 & 0 & 1 & 1 \\

& - & 1 & 0 & 1 & 0 & 0 & 0 \\

& - & 1 & 0 & 1 & 0 & 0 & 0 \\

& - & 1 & 0 & 1 & 0 & 1 \\

& - & 1 & 0 & 1 & 0 & 1 \\

& - & 1 & 0 & 1 & 0 & 1 \\

& - & 1 & 0 & 1 & 0 & 1 \\

& 0 & 0 & 1 & 1 & 1

\end{array}$$

イロト イヨト イヨト イヨト

.

# Division (Optional)

- Binary division is based on two basic operations:

- Generation of partial remainders

- Subtraction and shifting

- The quotient in division of two N-bits number is in general a N-bits number

$$\begin{aligned} R' \leftarrow 0 \\ \text{for } i = (N-1) \ \text{to } 0 \\ R \leftarrow \{R' << 1, A_i\} \\ D = R - B \\ \text{if } D < 0 \\ Q_i \leftarrow 0 \\ R' \leftarrow R \\ else \\ Q_i \leftarrow 1 \\ R' \leftarrow D \\ R \leftarrow R' \end{aligned}$$

## Array Divider (Optional)

• Hardware implementation of binary division

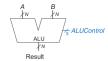

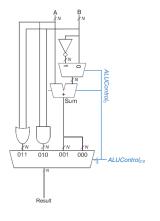

- Performs various mathematical and logical operations

- The desired result can be selected by ALUControl

イロン イ団 とくほとう ほんし

- Performs various mathematical and logical operations

- The desired result can be selected by ALUControl

- An ALU performing ADD, SUB, AND and OR

.

40 / 49

イロト イポト イヨト イヨト

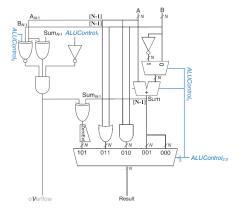

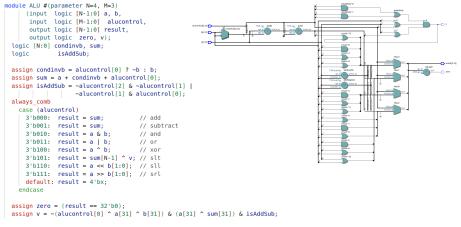

- Performs various mathematical and logical operations

- The desired result can be selected by ALUControl

- An ALU performing ADD, SUB, AND, OR and SLT

| ALUControl <sub>2:0</sub> | Function |

|---------------------------|----------|

| 000                       | Add      |

| 001                       | Subtract |

| 010                       | AND      |

| 011                       | OR       |

| 101                       | SLT      |

æ

イロト イポト イヨト イヨト

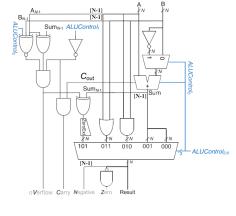

- Performs various mathematical and logical operations

- The desired result can be selected by ALUControl

- An ALU performing ADD, SUB, AND, OR and SLT

- Common flags: Negative, Zero, Carry and oVerflow

| ALUControl <sub>2:0</sub> | Function |

|---------------------------|----------|

| 000                       | Add      |

| 001                       | Subtract |

| 010                       | AND      |

| 011                       | OR       |

| 101                       | SLT      |

イロト イヨト イヨト

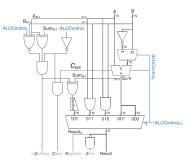

- Performs mathematical and logical operations

- ALUControl specifies the function

- Common Flags: N, Z, C, V

- Overflow detection

- Comparison depends on signed/unsigned

| Comparison | Signed                                         | Unsigned                 |

|------------|------------------------------------------------|--------------------------|

| =          | Z                                              | Z                        |

| ¥          | Z                                              | Z                        |

| <          | N⊕V                                            | $\overline{C}$           |

| $\leq$     | $Z + (N \oplus V)$                             | $Z + \overline{C}$       |

| >          | $\overline{Z} \bullet (\overline{N \oplus V})$ | $\overline{Z} \bullet C$ |

| ≥          | $(\overline{N \oplus V})$                      | С                        |

| ALUControl <sub>2:0</sub> | Function |

|---------------------------|----------|

| 000                       | Add      |

| 001                       | Subtract |

| 010                       | AND      |

| 011                       | OR       |

| 101                       | SLT      |

æ

43 / 49

イロト イヨト イヨト イヨト

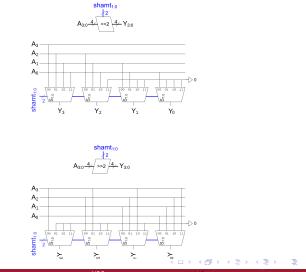

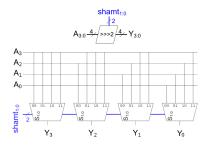

### Shifters

• Logical left and right shifts

USC

### Shifters

- Logical shifter

- Arithmetic shifter

- Arithmetic shift left multiplies by 2

- Arithmetic shift right divides by 2

- Overflow must be taken care of

- N-bit shifter can be built from N, N:1 MUXs

イロト イ団ト イヨト イヨト

æ

#### SystemVerilog (Optional)

- A typical ALU supporting add, sub, and, or, slt, sll, srl

- It has generates Zero and oVerflow signals

endmodule

イロト 不得 トイヨト イヨト

3

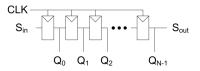

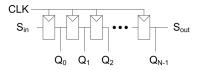

#### Serial-to-Parallel/Parallel-to-Serial Converters

- Shift registers act as serial-to-parallel converters

- The input is provided serially at Sin

- After N cycles, the last N inputs appear at  $Q_0 \dots Q_{N-1}$

イロト イヨト イヨト イヨト

.

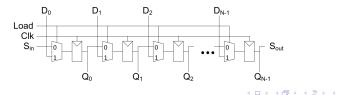

#### Serial-to-Parallel/Parallel-to-Serial Converters

- Shift registers act as serial-to-parallel converters

- The input is provided serially at  $S_{in}$

- After N cycles, the last N inputs appear at Q<sub>0</sub>...Q<sub>N-1</sub>

- Shift registers with parallel load can act in reverse

- The input  $D_0 \dots D_{N-1}$  is loaded in parallel

- $\bullet~$  Takes N cycles to shift out as parallel-to-serial converter

#### Counters

- N-bit counter composed of an adder and a resettable register

- There different approaches for designing various counters

- One easy way is to use an adder

- On each cycle, the counter adds 1 to the value stored in the register

- They are commonly used for dividing the clock frequency

イロト イ団ト イヨト イヨト