#### Floating point numbers and Memory

University of South Carolina

Introduction to Computer Architecture Fall, 2024 Mehdi Yaghouti

University of South Carolina (M. Y.)

• Fixed-point notation has an implied binary point

イロト イ団ト イヨト イヨト

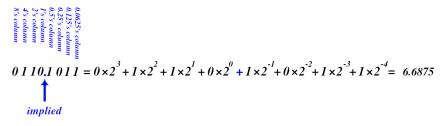

• Fixed-point notation has an implied binary point

```

0 \ 1 \ 10.1 \ 0 \ 1 \ 1 = 0 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0} + 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3} + 1 \times 2^{-4} = 6.6875

```

- Decimal fraction to Binary conversion

- Common negative power of two

0.5, 0.25, 0.125, 0.0625, 0.03125, ···

- Repeated multiplication by 2

< ロ > < 同 > < 回 > < 回 >

• Fixed-point notation has an implied binary point

```

0 1 10.1 \ 0 11 = 0 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0} + 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3} + 1 \times 2^{-4} = 6.6875

```

- Decimal fraction to Binary conversion

- Common negative power of two

0.5, 0.25, 0.125, 0.0625, 0.03125, ···

- Repeated multiplication by 2

- Binary to decimal conversion  $(b_N \dots b_k \bullet b_{k-1} \dots b_0)_2 = \sum_{i=0}^N 2^{i-k} b_{i-k}$

< ロ > < 同 > < 回 > < 回 >

• Sign/Magnitude

#

イロト イ団ト イヨト イヨト

æ

## Signed Fixed Point Representation

• Sign/Magnitude

#

• Two's complement

#

## Signed Fixed Point Representation

• Sign/Magnitude

#

• Two's complement

#

#### • Ua.b designates an unsigned fixed-point number with a integer and b fraction bits

• Qa.b designates an signed fixed-point number with a integer and b fraction bits

イロト イポト イヨト イヨト

• Compute 1.75 + (-1.625) using Q3.5 fixed-point numbers

イロト イヨト イヨト イヨト

- Floating-point numbers are analogous to scientific notation

- In general each rational number can be represented in scientific notation as,

$$\pm d_0.d_1d_2\cdots d_{n-1}d_n \times b^e$$

where b is the base (radix), e is the exponent and each digit  $0 \le d < b$

As we represent information in binary patterns, the radix is naturally taken as 2

Example:

$$-765_{10} = -101.1111101_2 \times 2^7$$

• As it can be seen the binary point can *float* at the expense of changing the exponent

▲□▶ ▲圖▶ ▲目▶ ▲目▶ - 目 - のの⊙

- ${\ensuremath{\, \bullet }}$  We call a representation normalized if there is only one digit 1 before the radix point

- Example:

$$-765_{10} = -101.1111101_2 \times 2^7$$

$$-765_{10} = -0.1011111101_2 \times 2^{10}$$

$$-765_{10} = -1.011111101_2 \times 2^9$$

- $\bullet\,$  In computer representation the radix is tacitly assumed to be 2

- The IEEE 754 is the widespread technical standard for floating point representation

イロン イ団 とくほとう ほんし

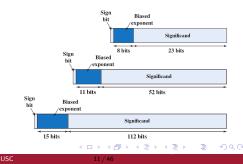

- The IEEE 754 standard uses a normalized notation with three fields:

- sign

- 0 for positive numbers

- 1 for negative numbers

- biased exponent

- Represents the sum of the actual exponent and a bias constant

- significand (mantissa)

- All bits to the right of the binary point

- $\bullet\,$  The 1 to the right of binary point is tacitly assumed for the sake of efficiency

- Single Precision: 32 bits

- Exponent Bias: 127

- Double Precision: 64 bits

- Exponent Bias: 1023

- Quad Precision: 128 bits

- Exponent Bias: 16363

• A floating-point number represented in IEEE 754 format can be calculated as,

$f = (-1)^S \times (1 + significand) \times 2^{exponent-bias}$

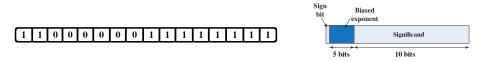

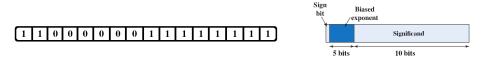

• Which number is given by the half-precision floating-point OXCOFF?

• A floating-point number represented in IEEE 754 format can be calculated as,

$f = (-1)^S \times (1 + significand) \times 2^{exponent-bias}$

• Which number is given by the half-precision floating-point OXCOFF?

イロト イヨト イヨト イヨト

• A floating-point number represented in IEEE 754 format can be calculated as,

$f = (-1)^S \times (1 + significand) \times 2^{exponent-bias}$

• Which number is given by the half-precision floating-point OXCOFF?

- exponent bias = 16 15 = 1

- significand =  $\sum_{k=3}^{10} 2^{-k} = 0.249023437$

$f = (-1)^1 \times (1 + 0.249023437) \times 2^1 = -2.498046874$

▲□▶ ▲圖▶ ▲目▶ ▲目▶ - 目 - のの⊙

• Encode the number -0.3 into 32-bits single precision format.

イロト イヨト イヨト イヨト

∃ 990

• Encode the number -0.3 into 32-bits single precision format.

# $\begin{array}{l} 0.3_{10} = (0.01001100110011001100110011 \cdots)_2 \\ = (1.00110011001100110011001)_2 \times 2^{-2} \end{array}$

イロト イヨト イヨト イヨト

$\bullet\,$  Encode the number -0.3 into 32-bits single precision format.

$$\begin{array}{l} 0.3 = (0.01001100110011001100110011 \cdots)_2 \\ = (1.00110011001100110011001)_2 \times 2^{-2} \end{array}$$

- Sign bit = 1

- Biased Exponent =  $127 2 = 125 = 01111101_2$

- Significand = 00110011001100110011001

- Single Precision Representation = 1011111010011001100110011001

- Single Precision Representation = 0XBE999999

- Absolute error  $\approx 1.8 \times 10^{-8}$

イロト イヨト イヨト イヨト

Special Values

| Number     | Sign | Exponent | Fraction                                |

|------------|------|----------|-----------------------------------------|

| 0          | Х    | 00000000 | 000000000000000000000000000000000000000 |

| ∞          | 0    | 11111111 | 000000000000000000000000000000000000000 |

| -∞         | 1    | 11111111 | 000000000000000000000000000000000000000 |

| QNaN       | Х    | 11111111 | 0 Non-zero                              |

| SNaN       | Х    | 11111111 | 1 Non-zero                              |

| Sub-Normal | Х    | 00000000 | Non-zero                                |

イロト イヨト イヨト イヨト

- Rounding Modes

- Round to nearest: The result is rounded to the nearest representable

- $\bullet$  Overflows are rounded up to  $\pm\infty$

- Underflows are rounded up to 0

- **Round toward**  $+\infty$ : The result is rounded up toward plus infinity number

- Round toward  $-\infty$ : The result is rounded down toward minus infinity number

- Round toward 0: The result is rounded toward zero

- Overflow : When the number magnitude is too large to be represented

- Underflow: When the number magnitude is too tiny to be represented

<四><日><四><日><日><日><日><日<<00</br>

- Add two single-precision float numbers a=0XF2D20004 and b=0X76407020.

- Extract exponent and significand

イロト イヨト イヨト イヨト

.

- Add two single-precision float numbers a=0XF2D20004 and b=0X76407020.

- Extract exponent and significand

- $b = 0 \ 11101100 \ 10000000111000000100000$

< ロ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 >

- Add two single-precision float numbers a=0XF2D20004 and b=0X76407020.

- Extract exponent and significand

- Add the leading 1 to significand

- $S_b = 1\,100000011100000100000$

イロト イポト イヨト --

- Add two single-precision float numbers a=0XF2D20004 and b=0X76407020.

- Extract exponent and significand

- Add the leading 1 to significand

- $Sig_b = 1\,100000011100000100000$

- Compare the exponents and shift the smaller significand if necessary 11101100

- -11100101

00000111

$Sig_a^\prime = 0000001101001000000000$

▲□▶ ▲圖▶ ▲目▶ ▲目▶ - 目 - のの⊙

- Add two single-precision float numbers a=0XF2D20004 and b=0X76407020.

- Extract exponent and significand

- Add the leading 1 to significand

- Compare the exponents and shift the smaller significand if necessary 11101100

- -11100101

00000111

Subtract or add significands together

1100000011100000100000

-000000011010010000000000

## 101111101100110000100000

<四><日><四><日><日><日><日><日<<00</br>

- Add two single-precision float numbers a=0XF2D20004 and b=0X76407020.

- Extract exponent and significand

- Add the leading 1 to significand

- **(2)** Compare the exponents and shift the smaller significand if necessary

- Subtract or add significands together

## 1100000011100000100000

## -000000011010010000000000

## 101111101100110000100000

イロト イヨト イヨト イヨト

• Add two single-precision float numbers a=0XF2D20004 and b=0X76407020.

- Extract exponent and significand

- Add the leading 1 to significand

- Ompare the exponents and shift the smaller significand if necessary

- Subtract or add significands together

- O Rounding the result if needed

<四><日><四><日><日><日><日><日<<00</br>

- Add two single-precision float numbers a=0XF2D20004 and b=0X76407020.

- Extract exponent and significand

- Add the leading 1 to significand

- Output the exponents and shift the smaller significand if necessary

- Subtract or add significands together

- So Far we have: 0 11101100 10111101100110000100000

- O Rounding the result if needed

- Assemble exponent and fraction back into floating-point format By eliminating the leading one :

## $0\,11101100\,01111101100110000100000$

Therefore: 0XF2D20004 + 0X76407020 = 0X763ECC20

イロト イヨト イヨト イヨト

- Registers built from flip-flops, stores small amounts of data

- Memory arrays can efficiently store large amounts of data

- Memories all provides the same generic functionality

- They differ in underlying structures, delay and area

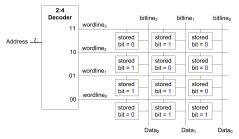

- Memory can be considered as a two dimensional array

- A memory with N-bit address and M-bit data has  $2^N$  rows and M columns

イロト イヨト イヨト

- Registers built from flip-flops, stores small amounts of data

- Memory arrays can efficiently store large amounts of data

- Memories all provides the same generic functionality

- They differ in underlying structures, delay and area

- Memory can be considered as a two dimensional array

- $\bullet$  A memory with  $N\mbox{-bit}$  address and  $M\mbox{-bit}$  data has  $2^N$  rows and M columns

- The number of rows and columns are called *depth* and *width* of the memory

< ロ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 > < 0 >

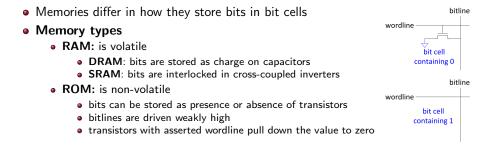

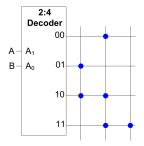

- Memory arrays are built as an array of bit cells

- For each combination of address bits the decoder asserts one wordline

- A bit cell is connected to the bitline, only if its associated wordline is asserted

イロト イヨト イヨト イヨト

.

イロト イヨト イヨト イヨト

31 / 46

æ

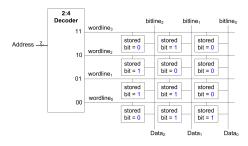

#### Memory read

- Initially the bitline is float (Z)

- 2 The wordline gets asserted and connects the bits in the row to the bitlines

イロト イヨト イヨト イヨト

32 / 46

æ

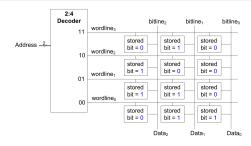

#### Memory Write

- The bitlines are strongly driven to 1 or 0 depending on the data

- In the wordline gets asserted and connects the bits in the bitlines

- In the bitlines overpower the content of each bit cell and overwrite the new value

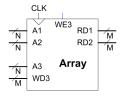

- As a black box, regardless of type, each memory is a multi-ported array of bits

- A Multiported memory can access several addresses simultaneously

- Writing into a memory address happens on the edge of the clock

イロト イ団ト イヨト イヨト

æ

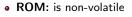

- Memories differ in how they store bits in bit cells

- Memory types

- RAM: is volatile

- ROM: is non-volatile

- Memories differ in how they store bits in bit cells

- Memory types

- RAM: is volatile

- DRAM: bits are stored as charge on capacitors

- SRAM: bits are stored in inter-coupled inverters

- ROM: is non-volatile

イロン イ団 とくほとう ほんし

## • Memories differ in how they store bits in bit cells

Memory Arrays

- Memory types

- RAM: is volatile

- DRAM: bits are stored as charge on capacitors

- The bit value will be destroyed by reading or charge leakage

- The contents must be refreshed every few milliseconds

- SRAM: bits are interlocked in cross-coupled inverters

- ROM: is non-volatile

イロト イヨト イヨト イヨト

## • Memories differ in how they store bits in bit cells

Memory Arrays

- Memory types

- RAM: is volatile

- DRAM: bits are stored as charge on capacitors

- The bit value will be destroyed by reading or charge leakage

- The contents must be refreshed every few milliseconds

- SRAM: bits are interlocked in cross-coupled inverters

- Bit values do not need to be refreshed

- Cross-coupling of inverters robustify them against noise

- ROM: is non-volatile

37 / 46

< ロ > < 同 > < 回 > < 回 >

#### University of South Carolina (M.Y.)

## Memory Arrays

- Memories differ in how they store bits in bit cells

- Memory types

- RAM: is volatile

- DRAM: bits are stored as charge on capacitors

- The bit value will be destroyed by reading or charge leakage

- The contents must be refreshed every few milliseconds

- SRAM: bits are interlocked in cross-coupled inverters

- Bit values do not need to be refreshed

Memory

Type

flip-flop

SRAM

DRAM

Cross-coupling of inverters robustify them against noise

Transistors per

Bit Cell

~20

6

usc

Latency

medium

fast

slow

Trade-off between area and speed

38 / 46

イロト イヨト イヨト イヨト

- Memories differ in how they store bits in bit cells

- Memory types

- RAM: is volatile

- DRAM: bits are stored as charge on capacitors

- SRAM: bits are interlocked in cross-coupled inverters

- ROM: is non-volatile

- presence or absence of transistors can be depicted as dots

イロト イヨト イヨト

- Memories differ in how they store bits in bit cells

- Memory types

- RAM: is volatile

- DRAM: bits are stored as charge on capacitors

- SRAM: bits are interlocked in cross-coupled inverters

- ROM: is non-volatile

- PROM: Programmable ROM

æ

イロト イヨト イヨト イヨト

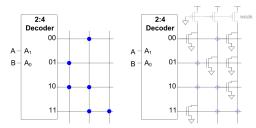

- Memories differ in how they store bits in bit cells

- Memory types

- RAM: is volatile

- DRAM: bits are stored as charge on capacitors

- SRAM: bits are interlocked in cross-coupled inverters

- ROM: is non-volatile

- PROM: Programmable ROM

- EPROM: Erasable Programmable ROM

- Use floating gate transistors

- Need high voltage to be programmed

- Need intense UV to be erased

<四><日><四><日><日><日><日><日<<00</br>

.

- Memories differ in how they store bits in bit cells

- Memory types

- RAM: is volatile

- DRAM: bits are stored as charge on capacitors

- SRAM: bits are interlocked in cross-coupled inverters

- ROM: is non-volatile

- PROM: Programmable ROM

- EPROM: Erasable Programmable ROM

- EEPROM: Electrically Erasable Programmable ROM

3

イロン イ団 とく ヨン イヨン

## Look Up Table (LUT)

- Memory arrays can also be used to perform combinational logic functions

- It looks up outputs for input combinations, matching addresses to truth table rows

- Memory arrays used for logic functions are called lookup tables (LUTs)

- A  $2^N\operatorname{-word}\times M\operatorname{-bit}$  memory can perform any combinational function of N inputs and M outputs

## SystemVerilog

- The following modules describes a  $2^N \times M bit$  RAM

- Writes occur at the clock edge only if the we is asserted

- Reads occur in a combinational manner

```

module ram #(parameter N = 6, M = 32) ( input logic clk,

input

logic we.

logic [N-1:0] adr.

input

input logic [M-1:0] din,

mem

СІКО

clk [

output logic [M-1:0] dout);

1'h0 CLR1

din[31..0]

logic [M-1:0] mem [2**N-1:0];

1'h1

ENA1 DATAOUT[31.0]

dout[31..0]

adr[5..0]

RADDR[5.0]

always ff @(posedge clk)

if (we) mem [adr] <= din:</pre>

WP

SYNC RAM

assign dout = mem[adr];

```

endmodule

イロト イ団ト イヨト イヨト

## SystemVerilog

- The following modules describes a  $2 \times 3 bit$  ROM

- Reads occur with in a combinational manner

```

module rom( input logic [1:0] adr,

output logic [2:0] dout)

always comb

Decoder0

dout[2]~not

dout

case(adr)

dout[2..0]

IN[1.0]

OUT[3_0]

adr[1..0]

2'b00: dout <= 3'b011:

dout[1]~not

2'b01: dout <= 3'b110:

2'b10: dout <= 3'b100:

2'b11: dout <= 3'b010:

endcase

endmodule

```

イロト イポト イヨト イヨト

.